CPU硬件安全技术入选本届世界互联网大会15项全球领先科技成果

11月7日,在浙江乌镇召开的第五届世界互联网大会主会场,清华微电子所所长魏少军教授发布了“CPU硬件安全动态检测管控技术”。这一全新的集成电路硬件安全技术入选本届世界互联网大会15项全球领先科技成果(排名不分先后)。

自2016年以来,世界互联网大会每年都发布由数十位国内外权威专家从全球近千个申报项目中评选出的约15项领先科技成果,这些成果通常被认为代表了当时互联网和信息技术相关领域的最高水平。

魏少军发布“CPU硬件安全动态检测管控技术”

CPU芯片的硬件安全是计算系统的安全根基。无法确保CPU的硬件安全,就无法保证运行其上的软件的安全,与之紧密关联的系统安全和网络安全则更无从谈起。长期以来,大家习惯认为硬件是安全的,从而在此基础上重点解决软件的安全问题。2018年初,“熔断”(Meltdown)和“幽灵”(Spectre)硬件漏洞曝光,全球主流高性能CPU芯片对这两个漏洞无一幸免,亿万台服务器、台式机、移动终端等因此受到严重的安全威胁,而这仅仅是CPU硬件安全问题的冰山一角。

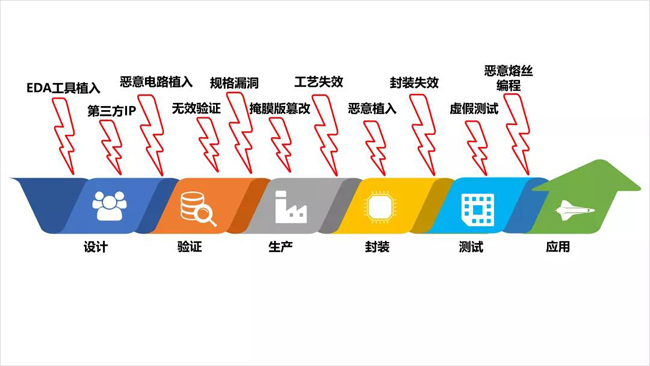

现代CPU动辄集成数百亿颗晶体管,只需要几十颗到上百颗晶体管就可以实现硬件木马,这些电路一旦被植入,想找出来就相当于“大海捞针”,非常困难。此外,现代CPU的设计、制造、封装、测试和部署的全过程,需要遍布全球成百上千家企业的参与才能完成,每个环节都可能引入硬件安全隐患,但让安全监管覆盖整个产业链的所有环节又是极其困难的。这些问题再加上不可避免的硬件技术漏洞,会对CPU芯片的安全带来极大挑战。国际学术界和工业界对软件安全的研究已持续了数十年时间,但对硬件安全,特别是对信息系统核心部件CPU芯片硬件安全的研究工作近几年才刚刚起步。

现代集成电路面临的严重硬件安全威胁

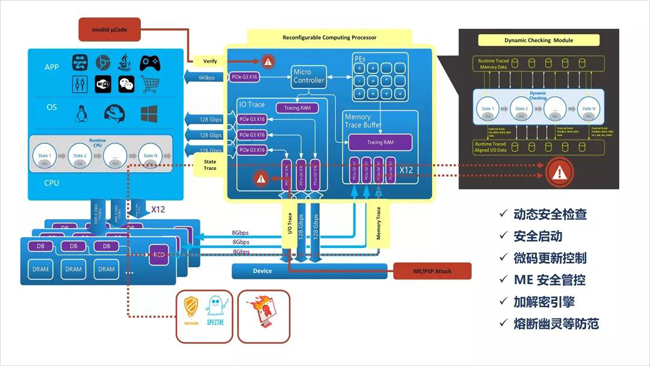

12年前,清华大学微电子所魏少军、刘雷波团队在开展可重构计算芯片研究工作时就已经注意到了这个问题。经过多年的持续科研攻关,魏少军、刘雷波团队提出了基于高安全、高灵活可重构计算架构的“CPU硬件安全动态检测管控技术”。该技术以CPU的行为跟踪为基础,通过快速分析和识别来判断CPU运行过程中是否存在损害其硬件安全的行为。这一技术克服了传统的在CPU芯片商业部署前进行安全检测无法有效应对软硬结合的复杂硬件安全攻击、难以发现全新硬件技术漏洞等先天不足(即“模拟环境下的离线检测”),在CPU芯片部署后上电运行的过程中,用一个独立的动态可重构芯片对CPU的所有重要行为,包括指令执行、内部状态变化、与外部存储及网络设备的数据交互,以及预测执行、缓存控制等微架构行为进行快速采样和实时分析(即“真实应用场景中的在线实时检测”)。无论是硬件木马、硬件漏洞(如“熔断”、“幽灵”)、硬件后门以及恶意利用硬件前门的行为(如恶意利用微码的行为),都会因CPU芯片行为异常而被该技术方案迅速发现,并能根据危害等级和用户安全需求进行管控。以上对CPU芯片的动态检测和实时管控是杀毒软件、软硬件“补丁”等传统安全方案无法实现的,可为用户的软件、系统和网络提供一个高度安全、可靠和可信的硬件计算环境。

“CPU硬件安全动态检测管控技术”示意图

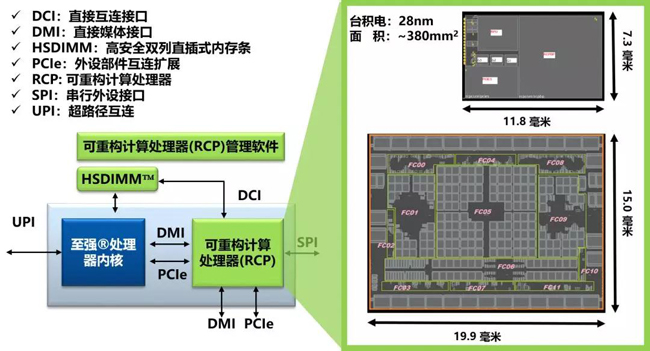

魏少军、刘雷波团队和中国电子旗下的澜起科技将 “CPU 硬件安全动态监测管控技术”用于新型X86架构CPU的研发,并于2018年7月研制成功了津逮高性能服务器CPU芯片。津逮CPU将可重构计算安全检测模块和传统的X86处理器内核结合起来,能对X86内核运行过程中的行为进行实时检测和管控。这是全球第一款用第三方的硅模块来动态监控处理器内核硬件安全状况的商用CPU芯片。联想、长城电脑、新华三等公司已完成了基于津逮CPU芯片的高性能商用服务器的研制,并将上市销售。

用可重构计算处理器动态监控处理器内核硬件安全状况

津逮高性能CPU芯片和联想SR651、长城JW920、新华三R4900商用服务器整机

我国目前有1500万台以上使用X86架构处理器内核的高性能服务器。云计算、大数据、物联网,移动互联等新兴应用绝大多数都以这类服务器为基础运算设备。然而,这些服务器的CPU芯片正无一例外面临着硬件安全上的巨大风险。“CPU 硬件安全动态监测管控技术”能为我国数据中心核心芯片的硬件安全保驾护航,使人们更加安全、更加放心地享受互联网上丰富多彩的创新科技成果。

近5年来,魏少军、刘雷波团队在硬件安全和密码芯片的研究上成绩卓著:发表高水平论文150余篇,其中50余篇IEEE Transactions论文、30余篇ISCA/DAC等顶级会议论文;授权发明专利60余项;出版专著3部;参与制定国家标准1项。相关硬件安全技术已在我国多个核心部门和重点企业取得批量应用。该团队曾获2015年国家技术发明二等奖、2017年电子学会技术发明一等奖、2015年中国专利金奖、2014年教育部技术发明一等奖等多项重要科技奖励。